CEA-Leti and STMicroelectronics have used IEDM 2025 in San Francisco to set out a route to fully monolithic silicon RF front-ends, combining high-performance active and passive devices on a single wafer through 3D sequential integration. The work targets next-generation RF and optical front-end modules for wireless and wireline communication systems.

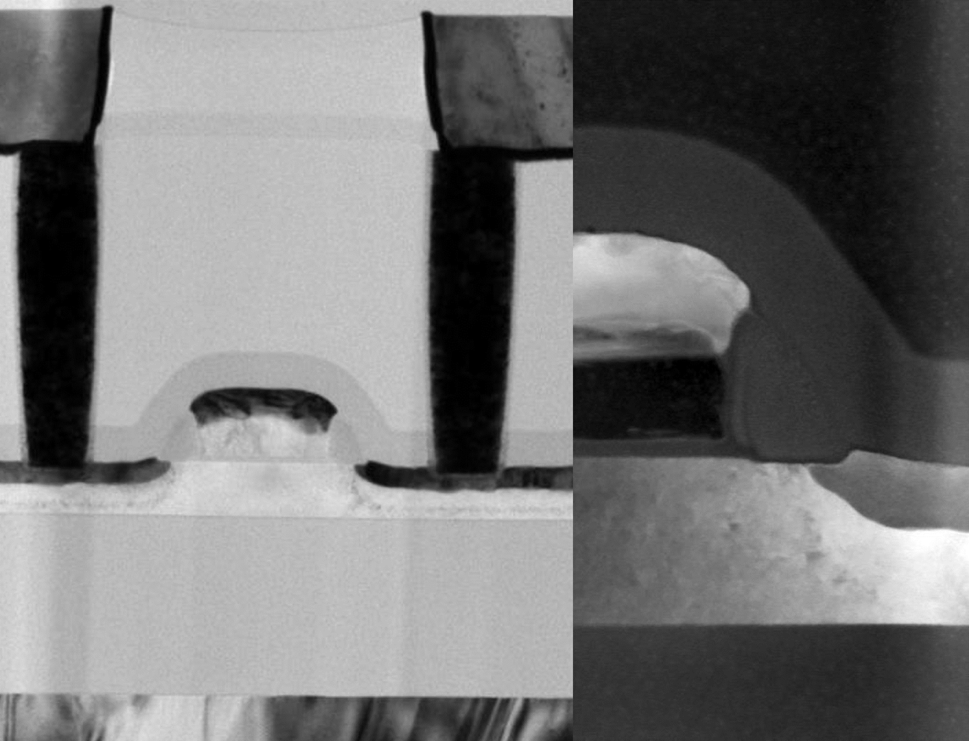

In their joint paper, “Unlocking High-Performance Si RF Platforms with SiGe HBT and RFSOI Switch Technologies,” the partners describe how silicon-germanium (SiGe) heterojunction bipolar transistors, RF SOI switches, and high-quality passives can be built directly on the same silicon wafer, rather than packaged or stacked as separate chips. The approach layers different device types sequentially, with process temperatures kept low enough to avoid degrading the performance of lower tiers.

The team reports that high-performance SiGe HBT devices have been engineered to withstand subsequent processing, while maintaining compatibility with top-tier fabrication steps. A localized trap-rich isolation layer provides RF isolation and linearity comparable to commercial trap-rich substrates, and is claimed to withstand thermal cycles up to 600 °C without compromising the underlying SiGe HBT layer. This is intended to cut parasitics and cost while driving integration density in RF front ends.

“Our team has shown that high-performance SiGe HBT has been conceived to be compatible with the top-tier fabrication steps, and that trap-rich isolation can be localized and thermally robust, and low-temperature (600°C) SOI switches can match state-of-the-art figures of merits,” said CEA-Leti’s Thibaud Fache, lead author of the paper. “These results pave the way to an all-silicon RF front-end module that is efficient and cost-effective.”

On the switching side, the work demonstrates RF Partially Depleted SOI switches fabricated at 600 °C instead of the more typical ~1000 °C. According to the team, this low-temperature process does not rely on new tools or exotic steps and is therefore close to industrial viability, given the more relaxed 600 °C thermal budget for the bottom tier. The result is described as high-quality, low-loss RF switching while maintaining the performance of the SiGe HBT layer beneath.

By extending silicon’s sequential integration playbook into the RF domain, the partners argue that fully integrated RF and optical front ends could simplify manufacturing and support more cost-effective deployment of dense wireless networks for smart cities, autonomous systems, and AI datacentres. The pitch is straightforward: fewer packages, fewer interfaces, and less parasitic baggage.

“This joint result demonstrates a credible path from advanced research to manufacturable solutions,” said ST’s Thomas Bordignon, co-author of the paper. “By combining CEA-Leti’s sequential integration know-how with ST’s RF technology expertise, we’re enabling the co-integration of state-of-the-art SiGe HBT, switches and passive devices, that are key elements of the FEM.”

CEA-Leti researchers are also flagging a separate IEDM presentation on high-performance SOI MOSFETs processed at just 400 °C, targeting “More Than Moore” applications from smart sensors to near-memory computing and RF devices. If both strands hold up in industrial flows, fully monolithic silicon RF platforms may finally move from conference slides to production roadmaps rather than remain a perennial R&D promise.