Satisfying mission assurance requirements for the most critical space programs, Microchip Technology’s (Nasdaq: MCHP) Radiation-Tolerant (RT) RTG4 Field- Programmable Gate Arrays (FPGAs) with lead-free flip-chip bumps have earned the Qualified Manufacturers List (QML) Class V status. As designated by the Defense Logistics Agency (DLA), QML Class V is the highest level of qualification for space components and a necessary step to satisfy mission assurance requirements on the most critical space missions such as human-rated, deep space and national security programs. Because QML qualifications are standardised based on specific performance and quality requirements governed by the DLA, customers can streamline their design and certification processes by using QML-qualified products.

In 2018, RTG4 FPGAs became the first RT FPGAs offering more than 150,000 logic elements to achieve a QML Class V qualification, and this next-generation solution with lead-free flip-chip bumps is the first of its kind to achieve QML Class V status. In advanced flip-chip package construction, such as that used in the RTG4 FPGA, flip-chip bumps are utilized to connect the silicon die and the package substrate. Lead-free bump material will help extend the longevity of the product, which is critical to space missions.

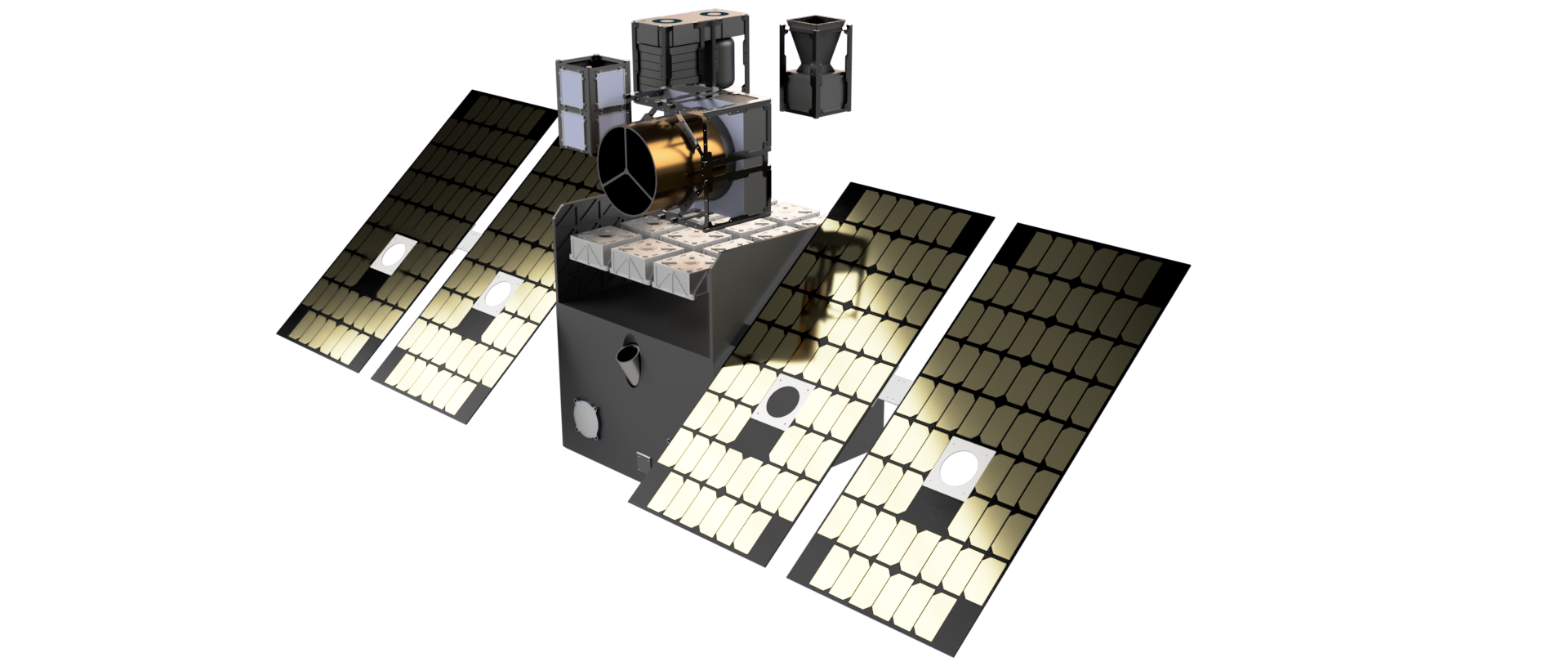

RTG4 FPGAs are designed to bring high levels of density and performance to space applications, saving cost and engineering efforts through low power consumption and immunity to configuration upsets. Unlike SRAM-based FPGA alternatives, the programming technology used in RTG4 FPGAs provides low static power, which assists in managing thermal issues common in spacecraft.

RTG4 FPGAs consume only a fraction of the total power compared to equivalent SRAM FPGAs, while exhibiting zero configuration upsets in radiation and thus requiring no mitigation, reducing engineering expenses and total system costs.

To achieve QML Class V qualification, the RTG4 FPGA with lead-free bump has undergone extensive reliability testing, enduring up to 2,000 thermal cycles from -65°C to 150°C junction temperature. The lead-free flip-chip bump interface connections passed MIL-PRF-38535 inspection criteria and exhibited no signs of tin whiskers. The flip-chip bump is inside the FPGA package, so there is no impact on the user’s design, reflow profile, thermal management or board assembly flow when converting to lead-free bump RTG4 FPGAs.